## Assembly, Simulation, Demos

| EEL 6744C JP Apps                                                     | 4 At           | Atmel Assembler<br>Directives        |  |

|-----------------------------------------------------------------------|----------------|--------------------------------------|--|

|                                                                       | Directive      | Description                          |  |

|                                                                       | ВУТЕ           | Reserve byte(s) to a variable.       |  |

|                                                                       | CSEG           | Code Segment                         |  |

| <u>AVR Assembler</u>                                                  | CSEGSIZE       | Program memory size                  |  |

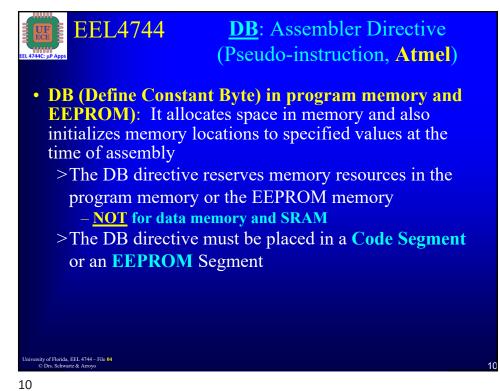

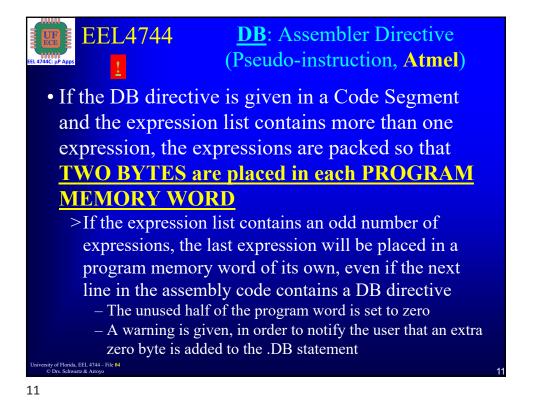

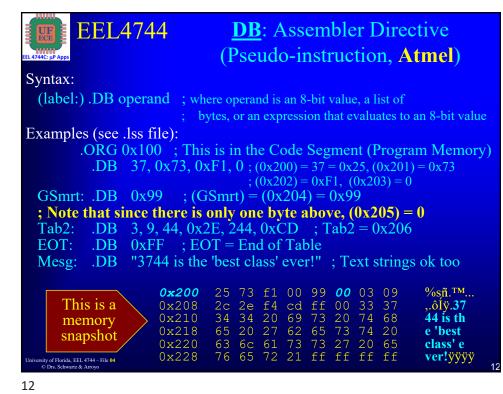

| Manual (Section 5                                                     | DB             | Define constant byte(s)              |  |

| has Assembler                                                         | DEF            | Define a symbolic name on a register |  |

| <b>Directives</b> )                                                   | DSEG           | Data Segment                         |  |

| Directives                                                            | DW             | Define Constant word(s)              |  |

| A.1                                                                   | ENDM, ENDMACRO | EndMacro                             |  |

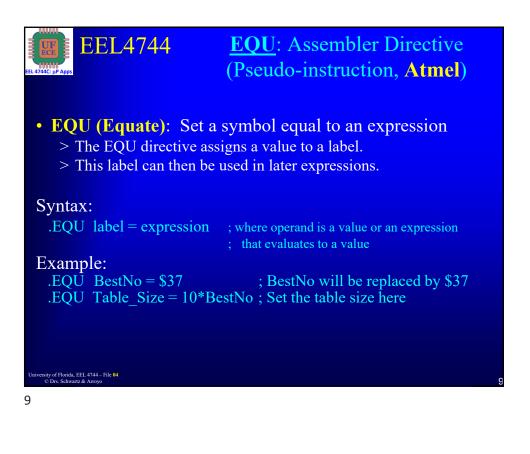

| Also, see                                                             | EQU            | Set a symbol equal to an expression  |  |

| <u>http://www.avr-asm-</u><br>tutorial.net/avr_en/begi                | ESEG           | EEPROM Segment                       |  |

| nner/DIREXP.html                                                      | EXIT           | Exit from file                       |  |

|                                                                       | INCLUDE        | Read source from another file        |  |

|                                                                       | LIST           | Turn listfile generation on          |  |

|                                                                       | LISTMAC        | Turn Macro expansion in list file on |  |

|                                                                       | MACRO          | Begin Macro                          |  |

|                                                                       | NOLIST         | Turn listfile generation off         |  |

| University of Florida, EEL 4744 – File 04<br>© Drs. Schwartz & Arroyo | ORG            | Set program origin                   |  |

| EEL4744C (JP Apps                                                    |                   | e Atmel<br>er Directives      |

|----------------------------------------------------------------------|-------------------|-------------------------------|

|                                                                      | Directive         | Description                   |

| <u>AVR Assembler</u>                                                 | SET               | Set a symbol to an expression |

| Manual (Section 5                                                    | ELSE,ELIF         | Conditional assembly          |

| <u>has Assembler</u>                                                 | ENDIF             | Conditional assembly          |

| <b>Directives</b> )                                                  | ERROR             | Outputs an error message      |

|                                                                      | IF,IFDEF,IFNDEF   | Conditional assembly          |

| Also, see                                                            | MESSAGE           | Outputs a message string      |

| http://www.avr-asm-                                                  | DD                | Define Doubleword             |

| tutorial.net/avr_en/begin                                            | DQ                | Define Quadword               |

| ner/DIREXP.html                                                      | UNDEF             | Undefine register symbol      |

|                                                                      | WARNING           | Outputs a warning message     |

|                                                                      | OVERLAP/NOOVERLAP | Set up overlapping section    |

| University of Florida, EEL 4744 – File 04<br>© Drs. Schwatz & Arrovo |                   |                               |

University of Florida, EEL 4744 – File 04 © Drs. Schwartz & Arroyo

6

## Assembly, Simulation, Demos

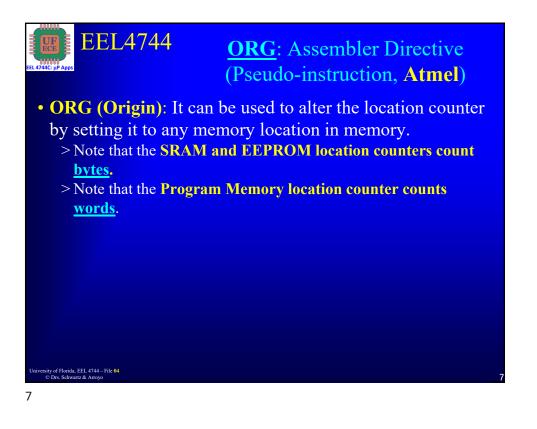

| ELATAAC: HP Apps                                                      | <b><u>ORG</u></b> : Assembler Directive<br>(Pseudo-instruction, <b>Atmel</b> )               |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| • ORG (Origin): It ca<br>to any location in me                        | n be used to alter the location counter by setting it emory.                                 |

| Syntax:                                                               |                                                                                              |

| ORG expression                                                        | ; where operand is a 16-bit address or an<br>; expression that evaluates to a 16-bit address |

| Example:                                                              |                                                                                              |

| .DSEG ; Start data se                                                 | egment                                                                                       |

| .ORG 0x2000                                                           | ; Set SRAM address to 0x2000                                                                 |

| Total: .BYTE 1                                                        | ; Reserve a byte at SRAM address 0x2000                                                      |

| .CSEG                                                                 |                                                                                              |

| .ORG 0x0200                                                           | ; Set Program Memory address to 0x200                                                        |

| MAIN: ldi r16, 0xF                                                    | ; Do something                                                                               |

| University of Florida, EEL 4744 – File 04<br>© Drs. Schwartz & Arroyo |                                                                                              |

| µР Арря       | LDI – Load Immediate                                                                 |

|---------------|--------------------------------------------------------------------------------------|

| Examples:     |                                                                                      |

| ldi r16, 27   | ; Load 27 (0x1B) into register r16, <i>r16 <b>←\$1B</b></i>                          |

| ldi r17, 0x34 | ; Load 0x34 into register r17, <i>r17 <b>&lt; \$34</b></i>                           |

| clr r31       | ; Clear Z high byte, <b>r31 ← 0</b>                                                  |

| ldi r30,\$F0  | ; Set Z low byte to \$F0 (0x and \$ are hex prefixes)<br>; <i>r30 ←</i> \$ <i>F0</i> |

| lpm r17, Z    | ; Load constant from Program memory pointed<br>; to by Z, <i>r17 &lt;- (Z)</i>       |

| lpm           | ; Load constant from Program memory pointed                                          |

|               | ; to by Z (notice with no operand, the default is r0),<br>; $r0 \leftarrow (Z)$      |

| lpm r18, Z+   | ; $r18 \leftarrow (Z), Z^{++} [Z^{++} \text{ means } Z \leftarrow Z^{+1}]$           |

| ldi ZL, low(T | able<<1) ; Load ZL with low address of Table                                         |

| ldi ZH, high( | Table<<1) ; Load ZH with high address of Table                                       |

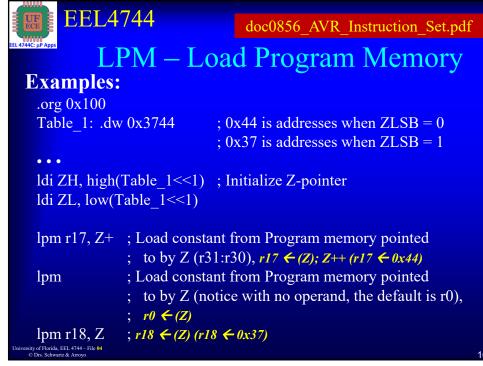

|                                                                                                                                                                                           | EEL4     | 744 doc0856 AVR Instruction Set.pdf                                            |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------|--|--|

| EEL 4744C: μP Apps                                                                                                                                                                        | L        | D – Load Indirect from Data                                                    |  |  |

| <b>Examples:</b> Space to Register                                                                                                                                                        |          |                                                                                |  |  |

| clr                                                                                                                                                                                       | r29      | ; Clear high byte of Y (Y = r29   r28), $r29 \leftarrow 0$                     |  |  |

| ldi                                                                                                                                                                                       | r28,\$37 | ; Set low byte of Y to \$37 (0x and \$ are hex prefixes), $r28 \leftarrow $37$ |  |  |

| ld                                                                                                                                                                                        | r0,Y+    | ; Load r0 with data at address \$37 (Y post increment),                        |  |  |

|                                                                                                                                                                                           |          | ; $r\theta \leftarrow (Y), Y^{++}$                                             |  |  |

| ld                                                                                                                                                                                        | r1,Y     | ; Load r1 with data at address \$38, $r1 \leftarrow (Y)$                       |  |  |

| ldi                                                                                                                                                                                       | r28,\$42 | ; Set low byte of Y to \$42, <i>r28</i> <b>&lt;</b> <i>\$42</i>                |  |  |

| ld                                                                                                                                                                                        | r2,Y     | ; Load r2 with data at address \$42 (since $r29 = 0$ ), $r2 \leftarrow (Y)$    |  |  |

| ld                                                                                                                                                                                        | r3,-Y    | ; Load r3 with data at address \$41 (Y pre decrement)                          |  |  |

|                                                                                                                                                                                           |          | ; Y, $r3 \leftarrow (Y)$ [Y means Y $\leftarrow$ Y-1]                          |  |  |

| ldd                                                                                                                                                                                       | r4,Y+2   | ; Load r4 with data at address \$43, r4 $\leftarrow$ (Y+2)                     |  |  |

| <ul> <li>Note that for loading with Y and Z, the ldd instruction lets you add up to 63 to Y or Z (%11 1111 = 63, i.e., a 6-bit post increment)</li> <li>There is NO ldd with X</li> </ul> |          |                                                                                |  |  |

| 15                                                                                                                                                                                        |          |                                                                                |  |  |